半导体笔记

0. 推荐书目

1.《半导体物理与器件》--- 施敏

2.《固体物理》 --- 黄昆

3.《CMOS模拟电路设计》--- 拉扎维

4. RF 射频电路设计

5. logic 电路设计 --- 有 SRAM 即可

6. 《Inside NAND Flash Memory》

7. 信息论

8. 自动控制原理 --- 会一种

9. 半导体可靠性评估

10. Fundamental Digital Test

- Asad Abidi 发表的论文

1. 半导体物理的一些理解

1.1 PN Junction

理想二极管方程:

齐纳击穿(Zener Breakdown) → 可恢复 → 隧穿 → BTBT

雪崩击穿(Avalanche Breakdown) → 不可恢复 → 碰撞

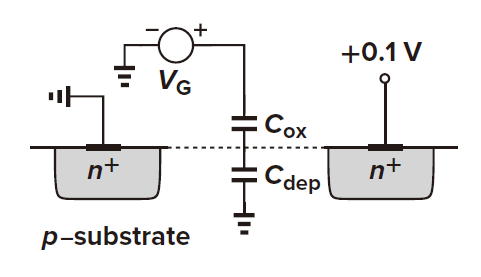

1.2 MOSFET

MOSFET 可以看作是一个漏电的可变电容,时间短为可变电容,时间长则漏电。

MOSFET 是一个电压控制型电流源,电压激发的器件其电流为指数型曲线。

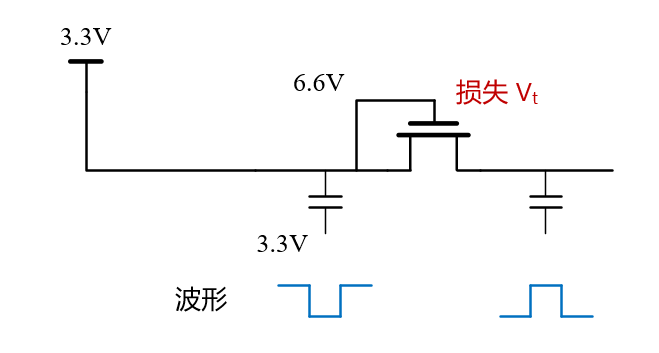

(需公式理解)N管不传高压,有Vt损失,P管可传高压,没有Vt损失。

(B比较小,容易扩散,传高压发热使结变大,有 Rel Concern)。

Treshold Voltage:

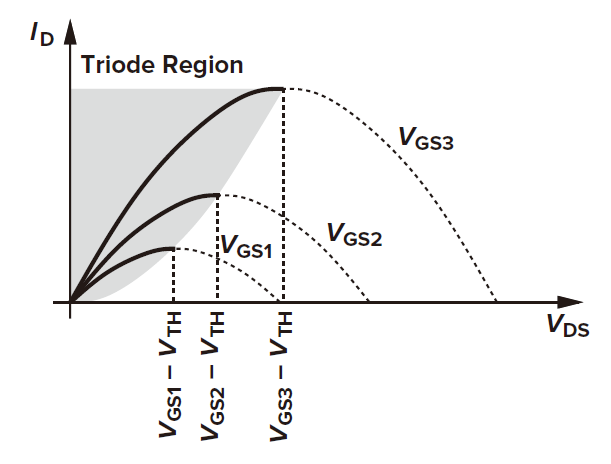

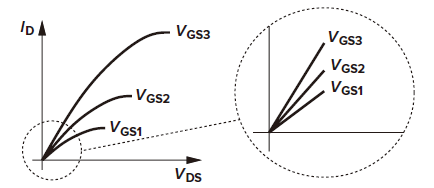

非饱和区电流公式: (三极管区,线性区)

当

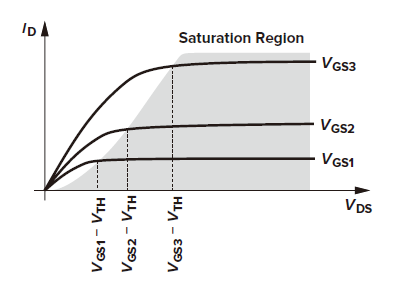

饱和区电流公式: 饱和 MOS 可视作电流源。

式中的

MOS 的 Overdrive Voltage:

上述公式也被称为设计公式,即知道电流和管子的尺寸,就可以反推电压。

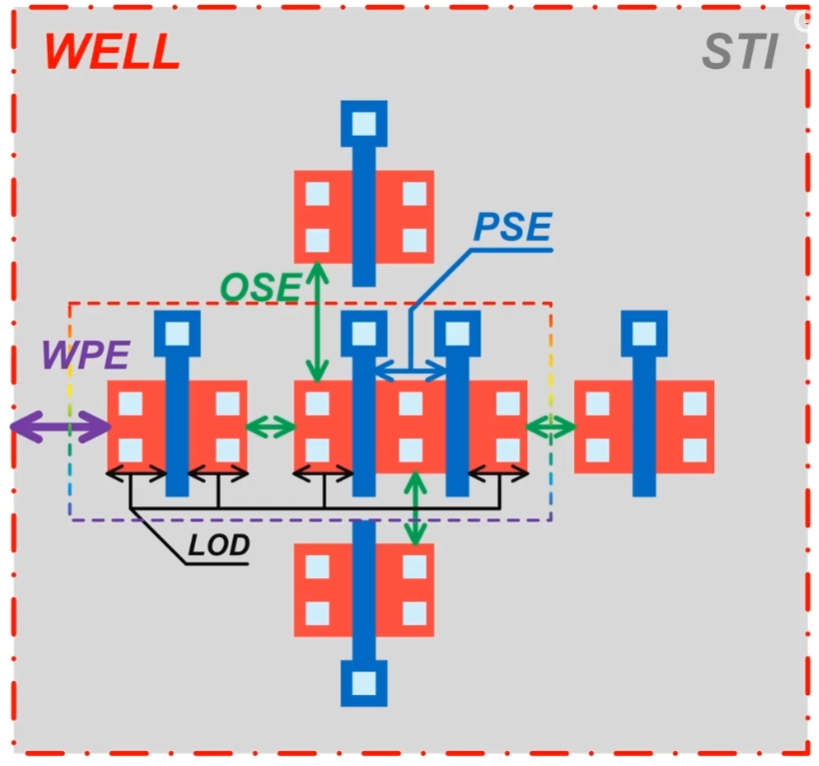

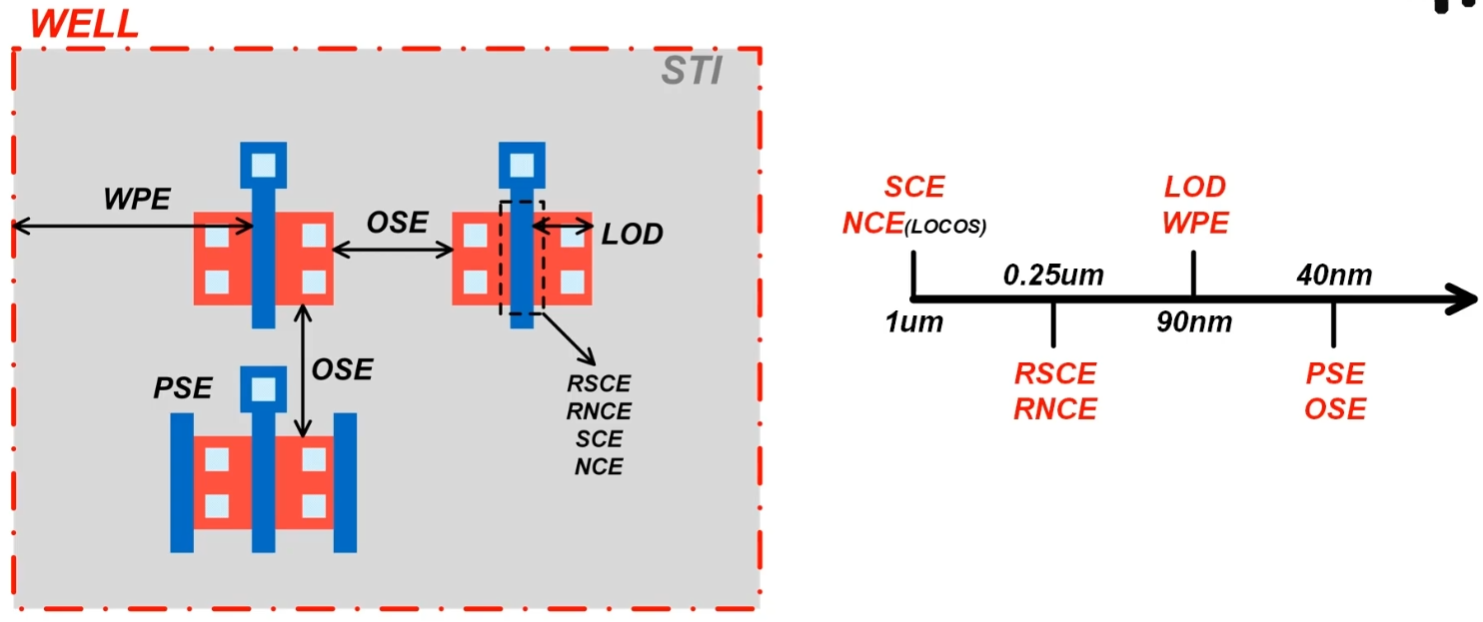

1.3 MOSFET 的十个寄生效应

DANGER

之后补充以下所有效应的具体公式

1.3.1 Long Channel

Body Effect, Pinch Off, Saturation

1.3.2 Avoid

Short Channel Effect, DIBL, PuchThrough

1.3.3 Parasite Effect

Tunneling, BTBT, GIDL, HCI

(BTBT, GIDL: 从 Id-Vg Curve 能看出来,从 Is-Vg Curve 看不出来)

1.3.4 Other Effect

REF: https://www.bilibili.com/video/BV18spre7E7u/

1.4 Note

高低频电路分界线:

DANGER

弛豫现象:待补充

2 Analog Circuit

2.1 小信号模型

2.2 ESD

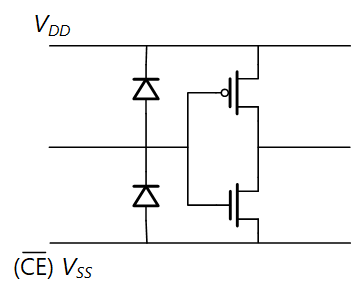

2.2.1 Type I : Control and I/O Pin

Openshort test,通电流,应看到 0.7V。 所以 CE Pin 在图中位置,芯片大部分时间是不工作的,通高压让电路关闭。

DANGER

然后介绍了这个电路和 Snapback。

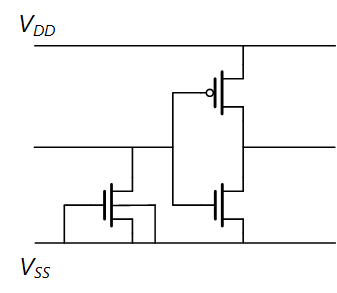

2.2.2 Type II: Power Pin

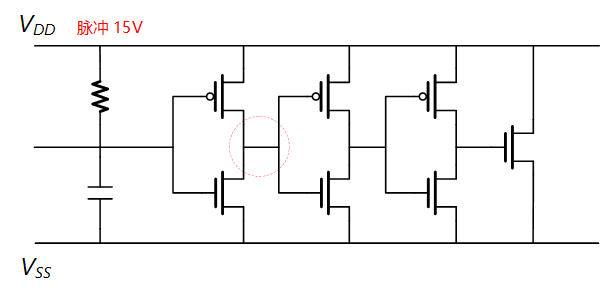

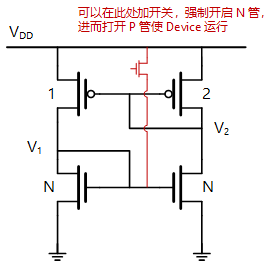

当 VDD 有脉冲 15V 时,红圈处约 12V,对于下一个非门,效果就更好。在足够短的时间内将脉冲电压导走,也就是开启最后那个管子,三级保证了时间短。

Powershort 测试 force 电流测电压,看到 0.7V 压降。 SPEC:0.2V ~ 2V。Powershort 的电压可以很低,保证没有管子打开,避免 Floating (例如 VCC 处为 0.2V)带来的瞬态电流过大,而这并不是 short。

2.2.3 Type III: HV Pin

ESD 电路需要抗各种频率,对于低频脉冲,当然希望降低 C,但是此情况下高频无法预防,所以 HV PIN 的 ESD 电路设计很难。

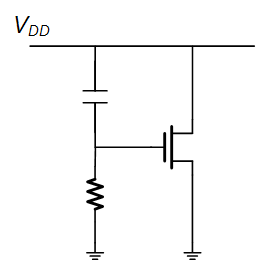

2.3 工作点 - 反相器

考虑上面这个电路的

对上述电路而言:

Analog 经常犯的问题:

- 选错工作点

- 非振荡电路发生震荡

- 振荡电路不震荡

2.4 Amplifier

2.4.1 两种放大器

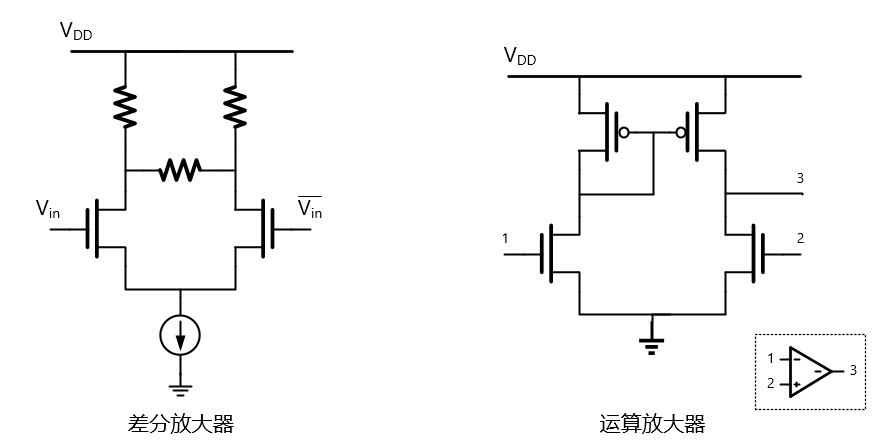

实际中很难应用差分放大器,因为取反信号很难得到。

差分放大器干掉同向毛刺,滤波器干掉最原始的的单信号的毛刺。

2.4.2 运算放大器

虚短:

虚断:

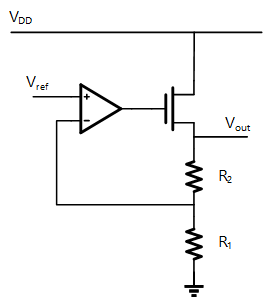

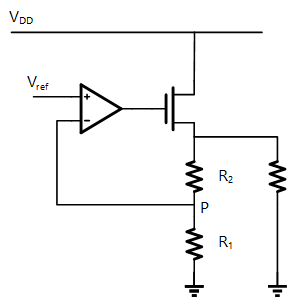

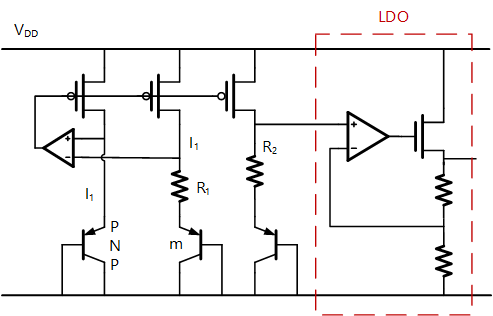

2.4.3 LDO

不带负载:

带负载:

如何带负载,会让

N 管 or P 管:如果用 N 管,

TRIM:

LDO 能耗高,轻电源不太能用,精准。

DCDC 不耗能,只有电感电容。(新能源汽车动能回收?)

DANGER

- 需继续了解 LDO 和 DCDC

- 运算放大器正负符号确定

2.5 Voltage Reference

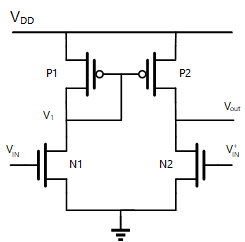

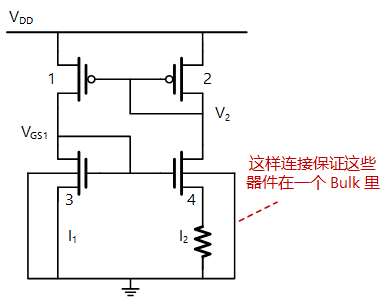

2.5.1 Current Mirror

电源很难做到和 V,T 完全无关,那么:

- 威尔逊电流源 → 与 V 无关

- Bandgap → 与 T 无关

2.5.2 Wilson Current Mirror

DANGER

当电流镜工作时:

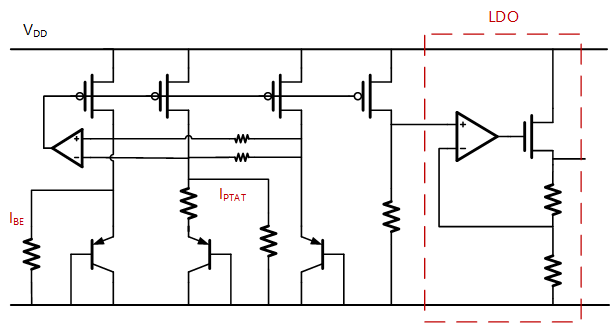

2.5.3 Bandgap

对于上图电路:

DANGER

这里的推导不太能看懂,m是分流系数?

此时,

使

DANGER

补充

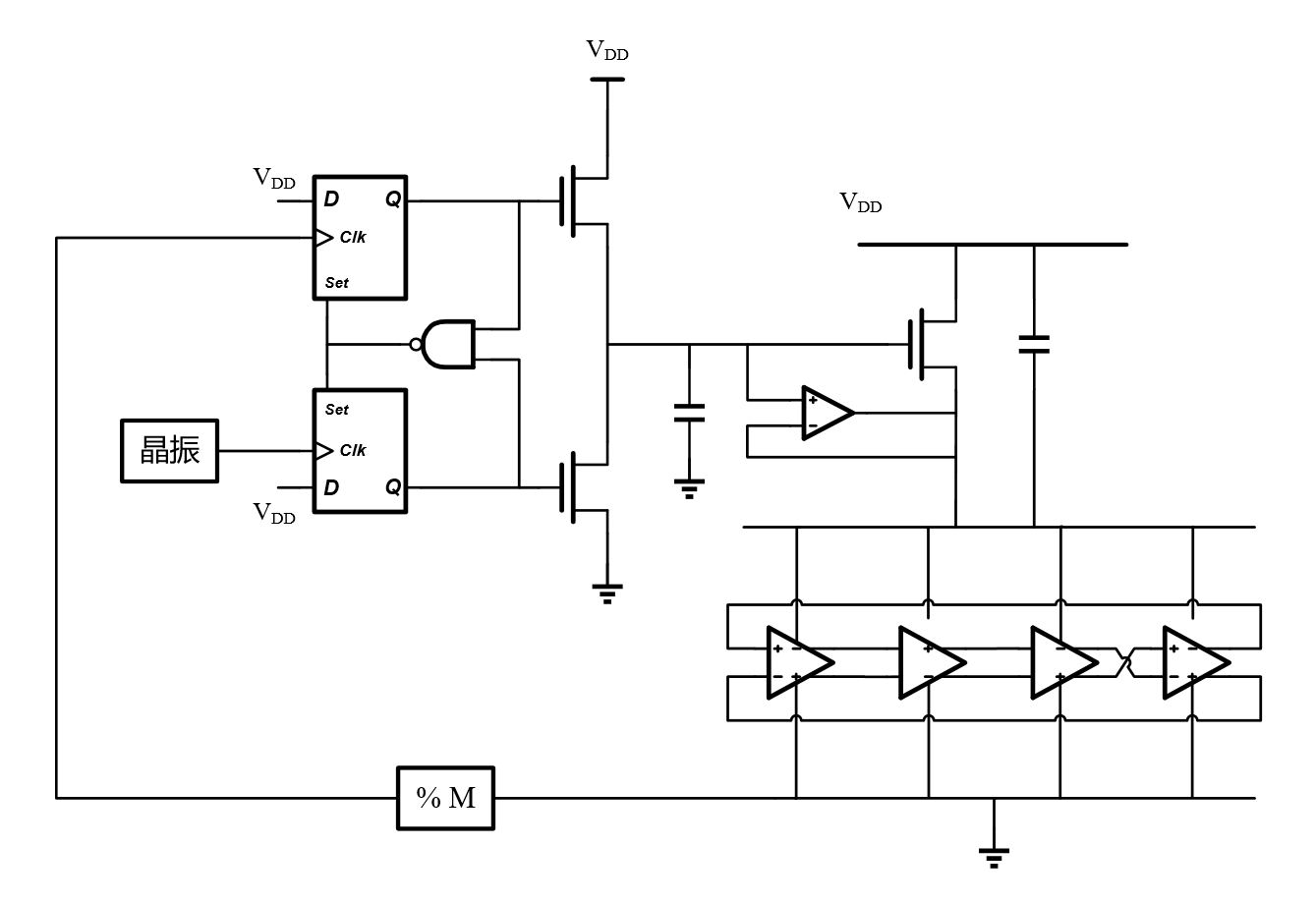

2.6 Clock

DANGER

开始介绍了环形振荡器。(待补充)

常见晶振频率:26MHz, 32MHz。

总体的效果是,芯片内部的 Clock 一直在追赶晶振 Clock。

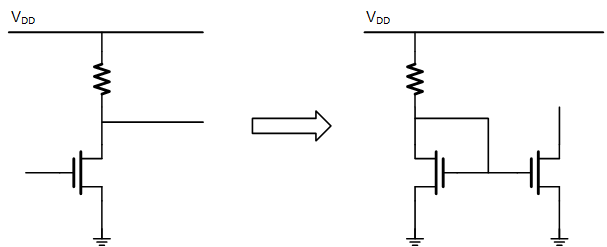

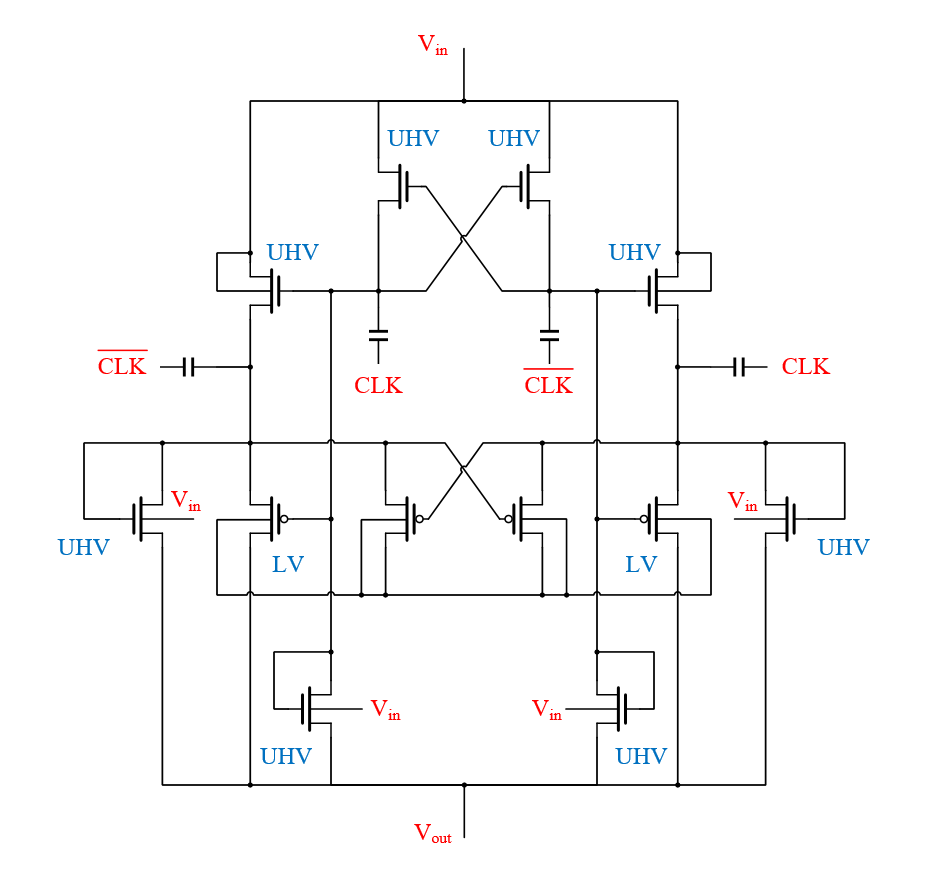

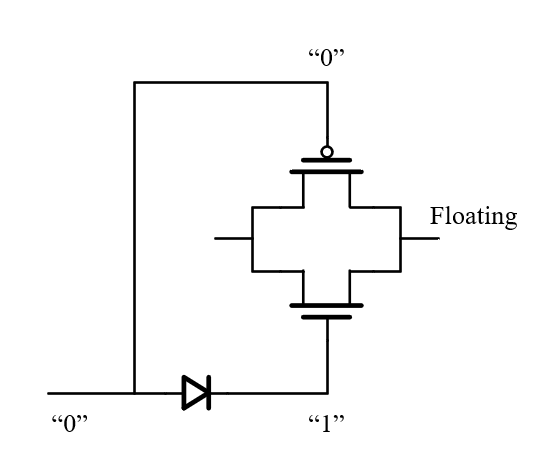

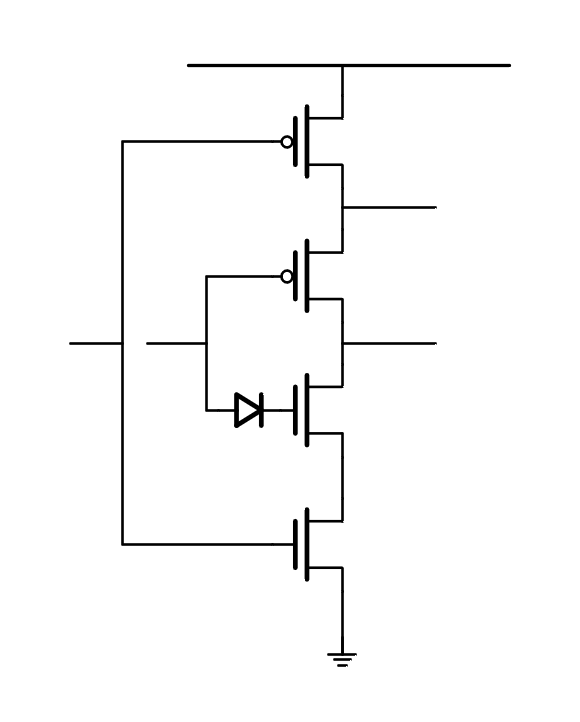

2.7 Charge Pump

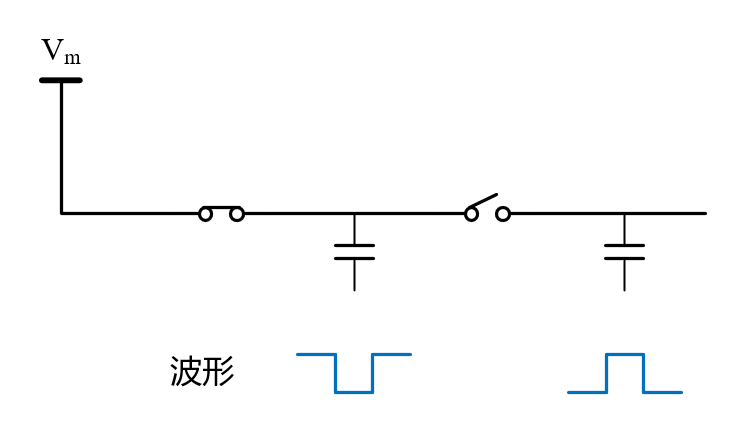

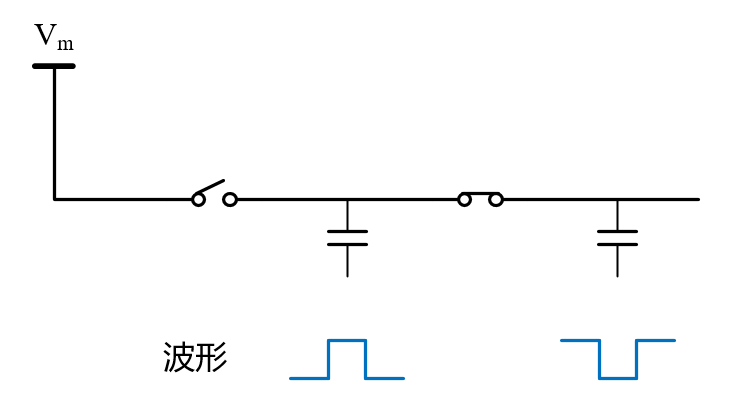

电容充电抬高电势,然后断开前面的开关,闭合后面的开关,将电压传过去,此时后面电容对应的节点是低电平。

但在实际电路中没有理想开关,所以只有如下电路:

Charge Pump 中的所有管子必中 Body Effect, 所以:

DANGER

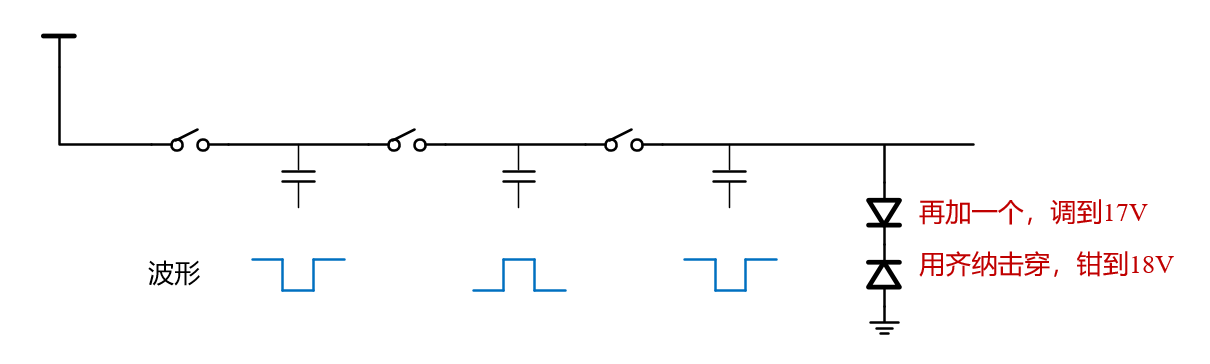

因此,Charge Pump 用 HVZ 管,后面就换了(需理解)。

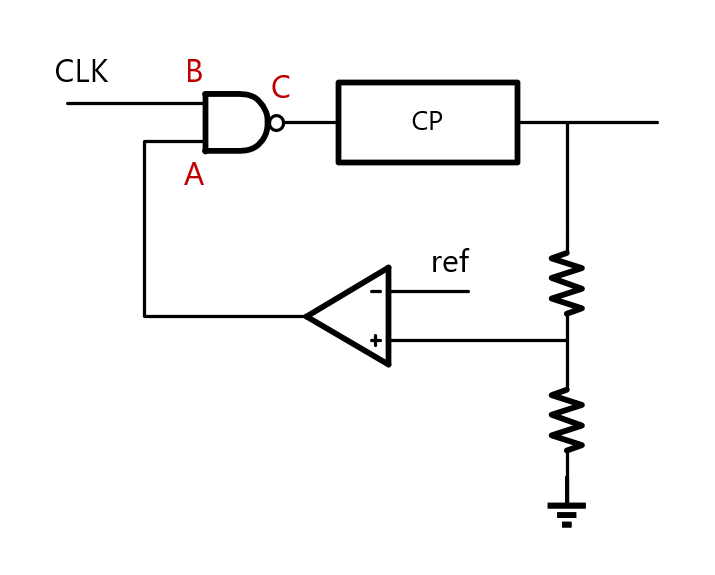

2.6.1 Charge Pump and Clock

| Control A | Signal In B | Signal Out C |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

即

管子的最高工作电压 ~30V,实际只能传 25.5V,这决定了 NAND Program 电压的极限。

2.7 Math

卷积,拉式变换,冲激函数,零点极点图。

在冲激函数下,输出时系统的响应。

对零点极点问题,即是让系统快速收敛。

相位裕度,让系统不震荡的情况下,有多少 margin,业标:

2.8 Other

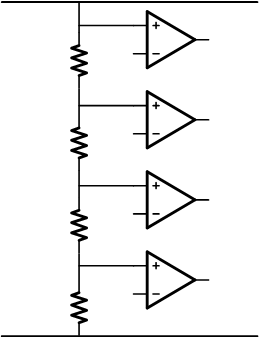

2.8.1 模拟信号转数字信号

2.8.2 串口转并口

NAND 内部很慢,但一口气并行就能匹配 CPU 的高频率。

DANGER

不太理解这个电路。

3 Logic Circuit

数字电路的核心是同步。

3.1 触发器

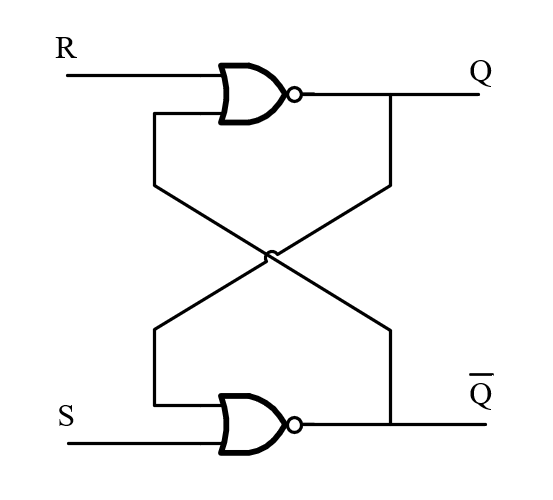

3.1.1 S-R 锁存器

| 0 | 0 | ||

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 |

TIP

注意:SR Latch 用两个 NAND 或者两个 NOR 都行,只是 truth table 不一样。

TIP

JK 触发器解决了 R,S 不能都是 0 的问题。

3.1.2 电平 D 触发器

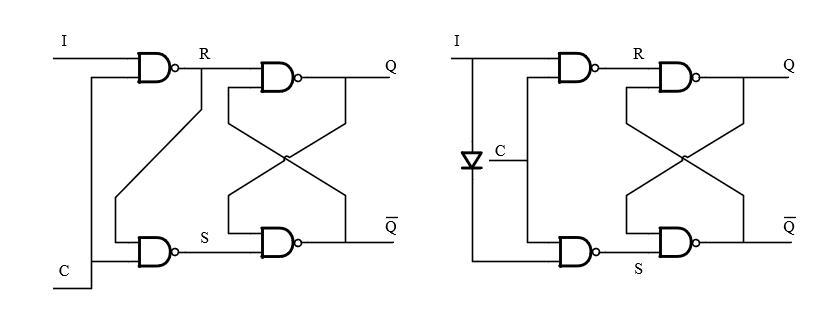

有两种画法:

| 0 | 0 | ||||

| 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1/0 | 0 | 1 | 1 |

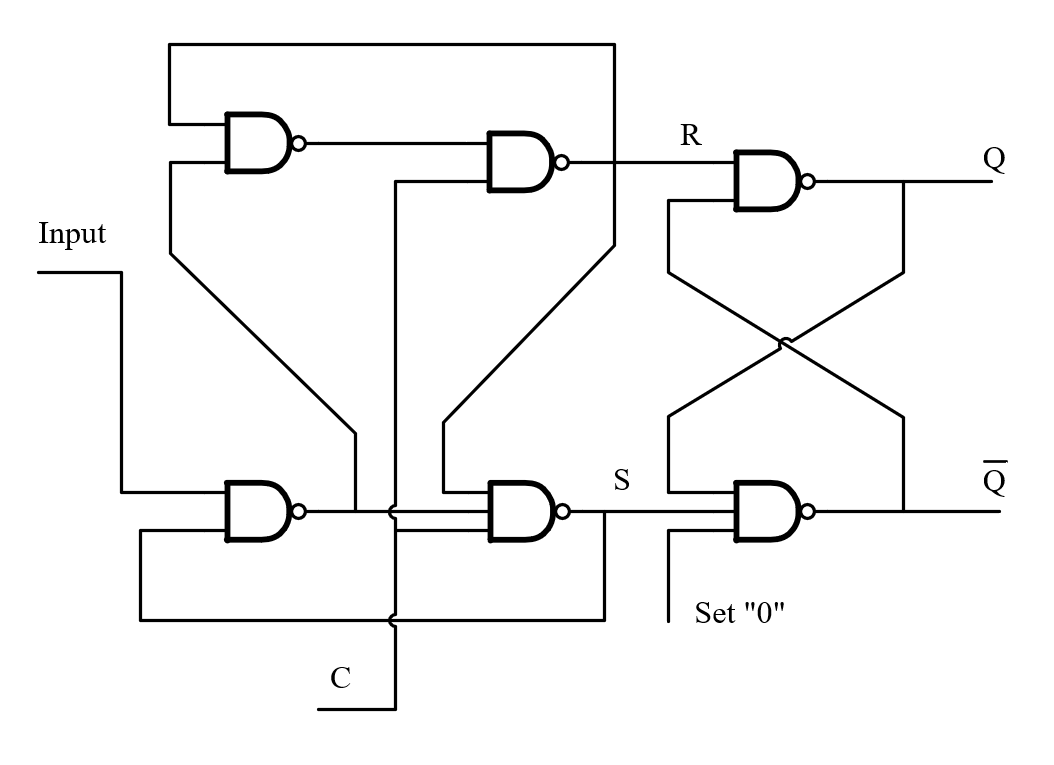

3.1.3 边缘 D 触发器

由于难以保证 N 管和 P 管的下拉、上拉能力一致,所以 D 触发器也不是完美的,但是周期间隔是绝对的,所以有了使用上升沿、下降沿的触发器。

TIP

传输门能实现类似的功能,但是传输门能输出高阻态。

TIP

三态输出

3.2 Setup time 和 Hold time

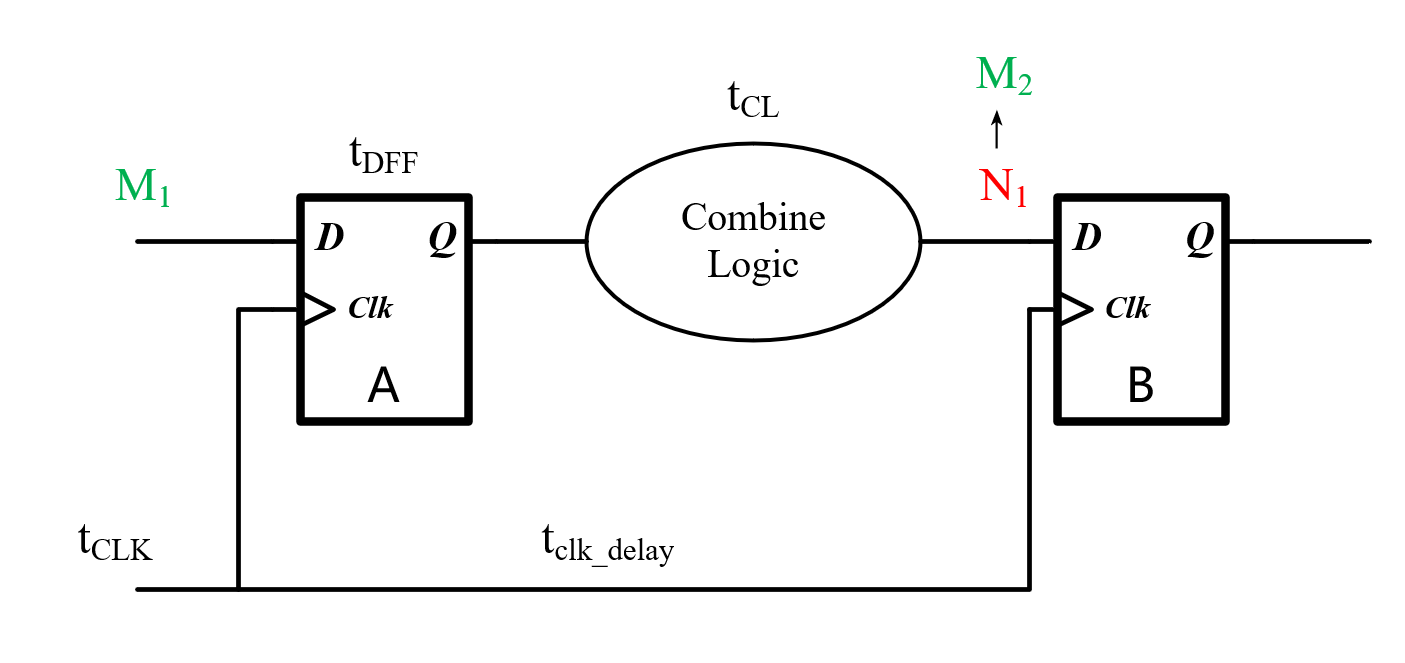

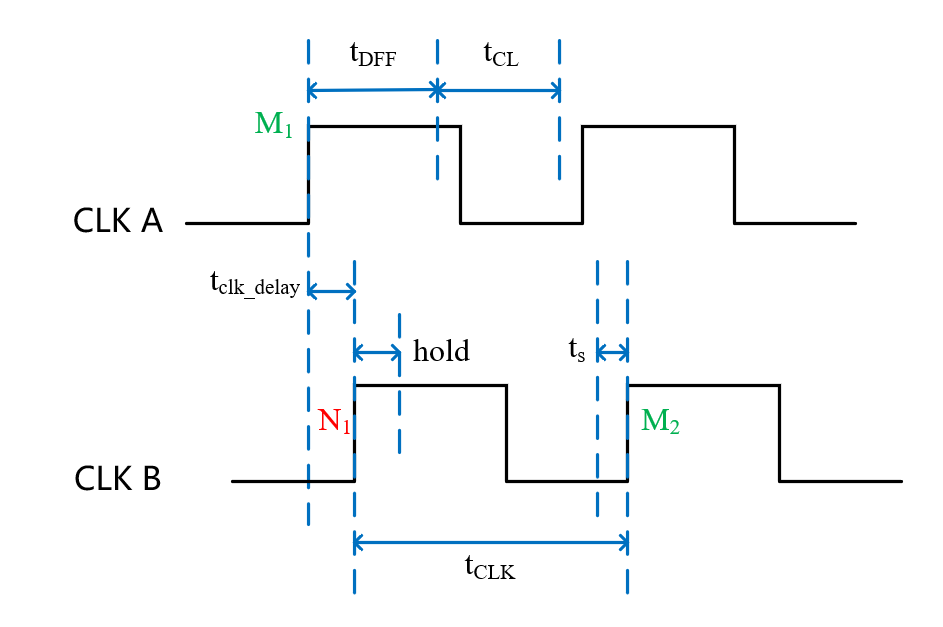

整个电路运行所需的时间大致如图:

对于两个 CLK:

因此

因为高频电路不好做,所以实际上都会想办法让

1.

改不了

2.

可以降频(

TIP

65 nm 及以下,尤其是 40 nm 以下,很难抓点,全是

TIP

DFT, 片选选择器,用于决定使用内部信号还是外部测试信号,但是牺牲面积和频率。(据传 Intel 没有 DFT)

| Test | Ratio | Comment |

|---|---|---|

| AC Train | ||

| DC Scan (Stuck) | ~90% | 对 timing 要求不高 |

| AC Scan | 10% | 高频 critical |

经验上,要测需要以小时计,由 pattern 影响:

1s --> 50%

10s --> 90%

1 hour --> 99%

3.3 功耗

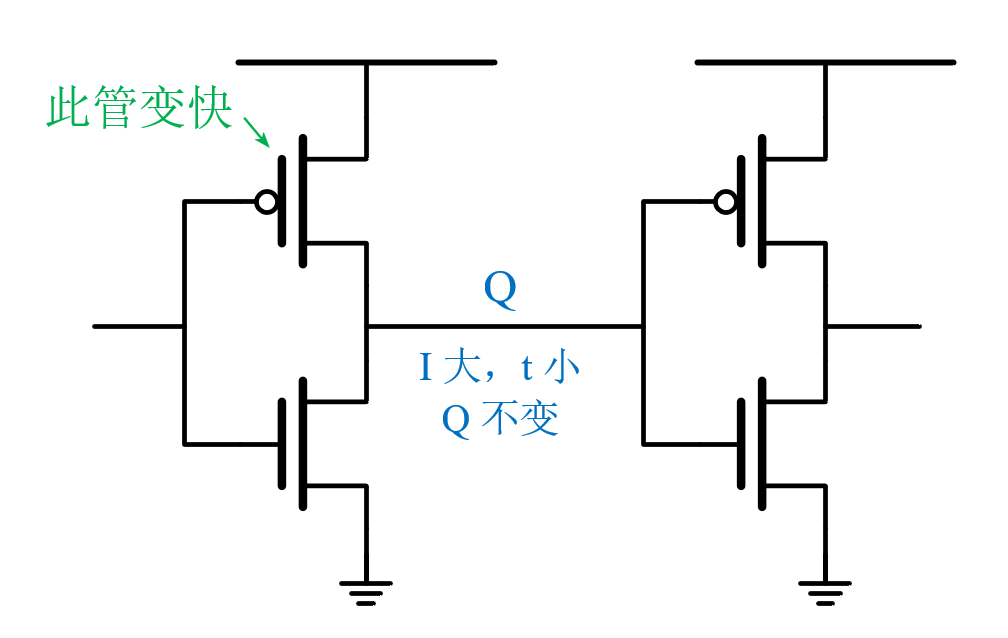

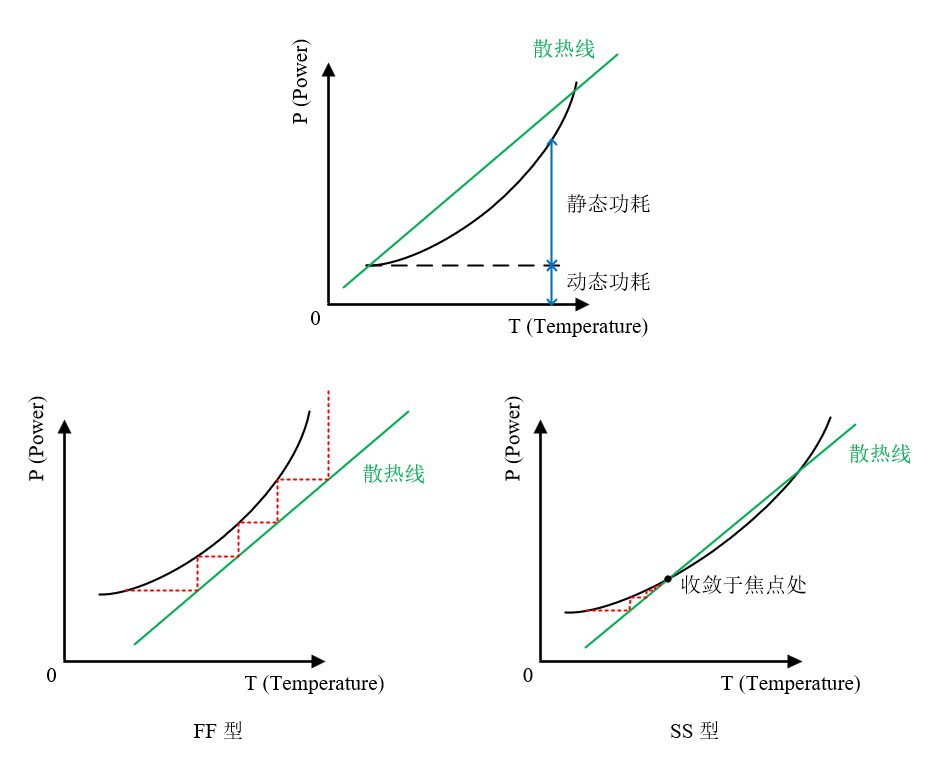

功耗分为静态功耗和动态功耗。静态功耗与 Device Speed 正相关(每个节点都为定制,即由

3.3.1 静态功耗计算

由于温度对

3.3.2 动态功耗计算

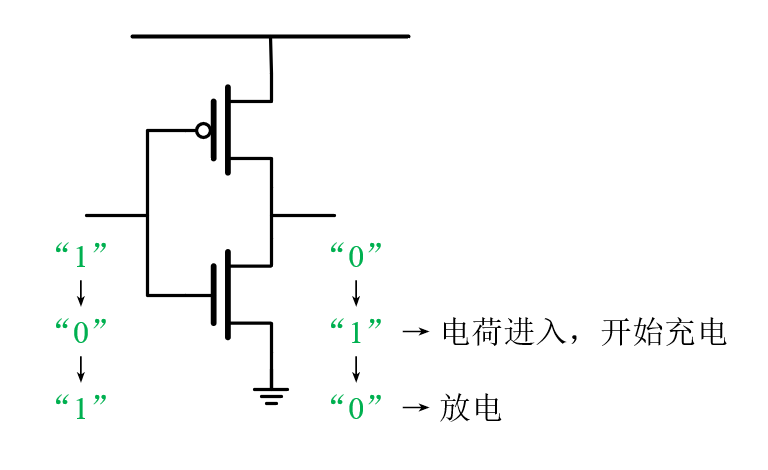

在 2T 周期内,由电荷

但动态功耗发热使静态功耗升高,测得的功耗为动态功耗 + 静态功耗。Sort 测不了动态功耗,因为测不了热直激。

对功耗和散热的分析:

为了有交点:

- 降低动态功耗

- 降

- 换散热板

1. Voltage Binning

但是有的芯片没法降频(没有市场),只能降电压,也就是 Voltage Binning。Qualcom 和联发科采用这种方法,市场不接受所谓低频版,所以全部调电压,营销上先卖低频版,再卖高频版。

另外 Qualcom 的芯片主要用于手机,不能太高温,产品可靠性要求也不高,所以也有需要降频降压机制来控制温度。

2. Frequency Binning

英特尔的 i3, i5, i7 即是采用 Frequency Bining,解决了良率问题,可以任意屏蔽核心,节省了研发和测试成本。

另外不做 Voltage Bining 也和升压带来的可靠性问题有关,SS corner 寿命差。

用户很难接受所谓的低频版,所以全部调电压,策略上先卖低频再卖高频.