Memory

1. NAND

DANGER

Memory 的核心是结构。 Memory 发展史:

NAND 最核心的参数:

VGVT的业标:(

3BL 技术的重点是一次充电做了两次 Verify,而不是减少了一次 PGM。因此要求 Cell 工作在线性区,保证能根据一定的 Verify 时间后,得到通过的电流是高于

几个效应:

- PVS:

即是 PGM pulse count。 - CD/CDU: CD uniformity

- Striation: 毛刺

- Distortion:椭圆

- Tilting:CH 斜了

- Background Pattern(SS)

- IVS: 由 SION 抓住电子所带来的 3eV 并不能稳定获得

- Coupling: Program 之后,每层 WL cover 的区域变小了,

- RTN

TIP

探讨了 PGM 应该从上往下还是从下往上:

从下往上 PGM,下面的 Cell 受到更大的 disturb。(需理解)

从上往下 PGM,只影响 E0,但是会隔绝 CH 电流,因为电子从 BL 来。

Single Deck:从上往下。

Double Deck: 从下往上,因为 deck 接头处隔绝电流太强。

TIP

然后介绍了 Voltage Sensing 到 Current Sensing。

UVVt 是 UV 光照了之后的 Vt。

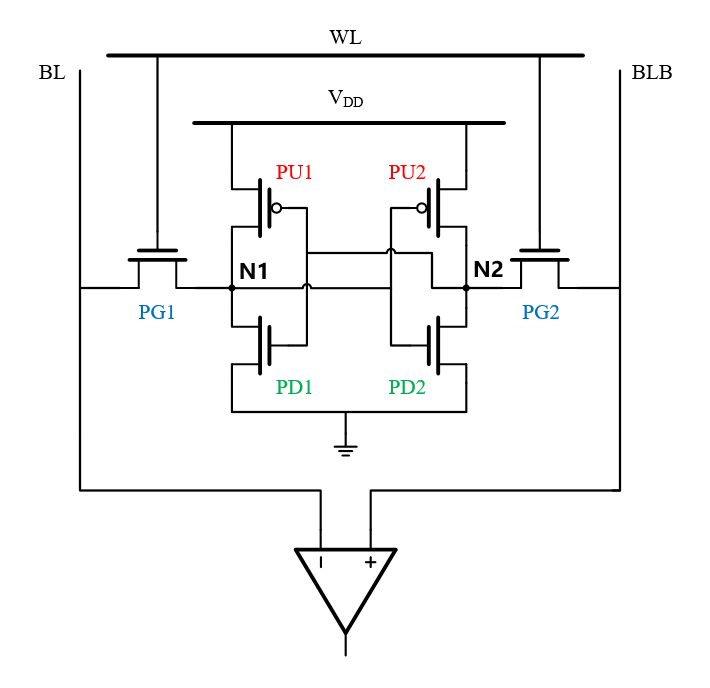

2. SRAM

写:左 0,右 1。

读:左

为了保证 Read 的时候不发生翻转,需要保证

由此:

SRAM 由于可能有 Read Failure, 所以需要 6N 和 8N 测试,保证没有读翻转:

- W0 R0,W1 R1,W0 R0

- W0 R0 R0, W1 R1 R1,W0 R0 R0

TIP

然后谈论了高速 I/O 的测试 Pattern。

SRAM 可以评估 Process 的 Uniformity, Logic 的测试器件就是 SRAM。

SRAM 的良率是 90%,那么 Logic 可以达到 95%(SRAM 比较密,Logic 的密度一般是它的1/2,defect 密度也为 1/2)。

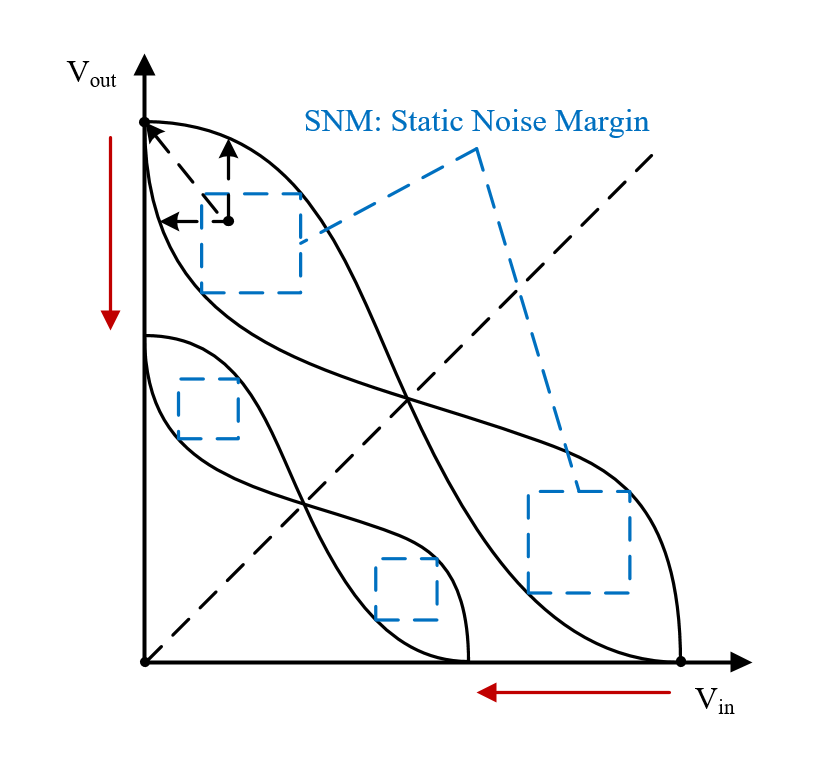

Butterfly Curve 可以缩放,即减小电压,此时 SNM 变小,也就是说可以用小

| Yield | 对应阶段 | |

|---|---|---|

| 90% | 研发 | |

| 90% | 0.9 | 试量产 |

| 90% | 0.8 | 量产 |

| 90% | 0.7 | TSMC |

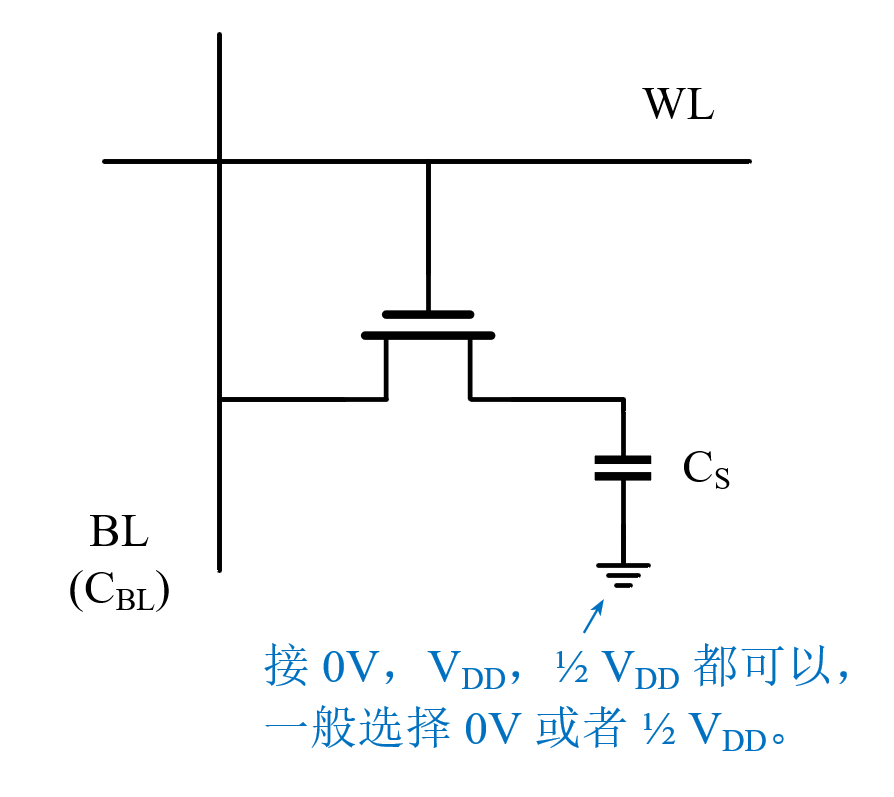

3. DRAM

DRAM RD 时 BL 电压: 0V (看升不升),

TIP

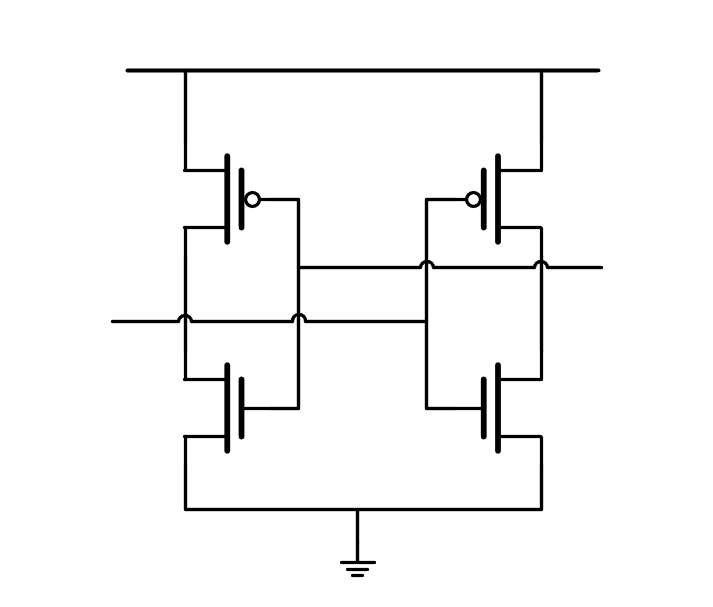

DRAM 的放大器:虽然结构很像 SRAM 但不是,注意 N : P = 1 : 1。

DRAM 的几个难点:

- C 使用

, ,介电层要越做越薄(只能改变 d),然后用 来降低隧穿。 - DRAM 中有几处电容,

和 : 很大而 很小,那 BL 可能用 0.55V 升到 0.6V 左右,Margin 很小。

- 有 MOS 管的情况下,就会有

,电容就漏电,因此要求 做到 量级,然而Nanoprobe 只能做到 。 - DRAM 放大器要求必须高度统一。(BL 版图很多 Dummy)

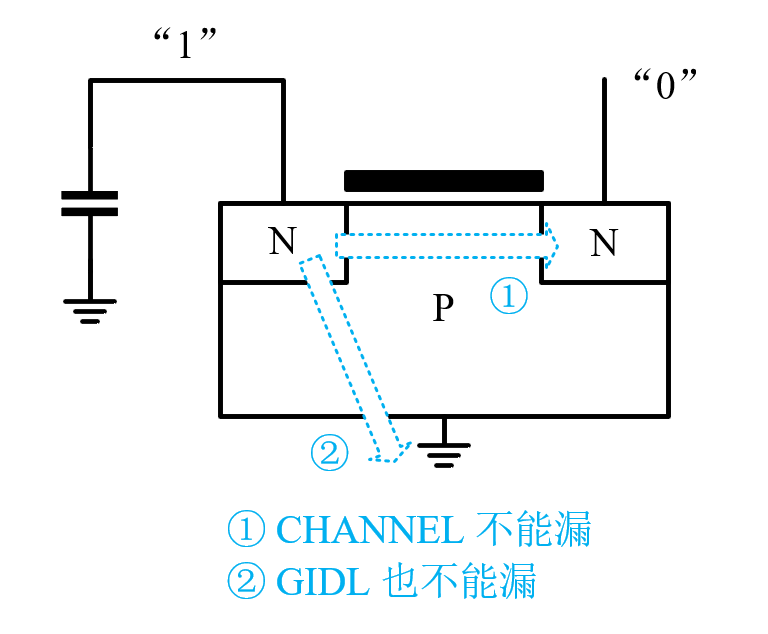

- BL Noise: ① CHANNEL 不能漏电。② GIDL 也不能漏电。C 是浮体(Floating),不怕 GIDL 怕 CHANNEL LEAKAGE,Bulk 可以灌电压。无非是反过来,都是怕 GIDL。X 使用了 Dual Gate(一个 Gate 拆成 Poly 和 W),功函数不一样,结变缓,隧穿降低。

TIP

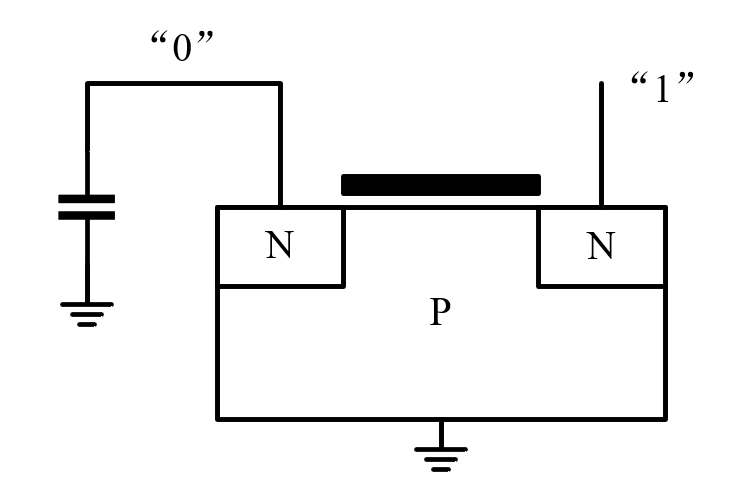

X 是平面结构,存 “0” 好但是存 “1” 差。

- 写 “1” 比写 “0” 难,前者是

,后者是 ,因此前者相比后者电流小。

| LT | HT |

|---|---|

DANGER

确认表格正确性

因此,对于 DRAM 的要求:

- Universal Curve 要大。

- 整个器件

和 的 distribution 都小,5 sigma 之内不 Fail。现在卡在 的展宽降不下来,GIDL 引起,没有很好的办法。